Gowin FPGA Quad JTAG Interfaces Offline Programmer

**User Guide**

UG301-1.1E,02/19/2020

#### Copyright©2020 Guangdong Gowin Semiconductor Corporation. All Rights Reserved.

No part of this document may be reproduced or transmitted in any form or by any denotes, electronic, mechanical, photocopying, recording or otherwise, without the prior written consent of GOWINSEMI.

#### Disclaimer

GOWINSEMI®, LittleBee®, Arora, and the GOWINSEMI logos are trademarks of GOWINSEMI and are registered in China, the U.S. Patent and Trademark Office, and other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders, as described at www.gowinsemi.com. GOWINSEMI assumes no liability and provides no warranty (either expressed or implied) and is not responsible for any damage incurred to your hardware, software, data, or property resulting from usage of the materials or intellectual property except as outlined in the GOWINSEMI Terms and Conditions of Sale. All information in this document should be treated as preliminary. GOWINSEMI may make changes to this document at any time without prior notice. Anyone relying on this documentation should contact GOWINSEMI for the current documentation and errata.

## **Revision History**

| Date       | Version | Description                            |

|------------|---------|----------------------------------------|

| 07/10/2019 | 1.0E    | Initial version.                       |

| 02/19/2020 | 1.1E    | Programming security key added. (GW2A) |

## **Contents**

| Co         | ntents                                                                                  | i     |

|------------|-----------------------------------------------------------------------------------------|-------|

| Lis        | st of Figures                                                                           | ii    |

| Lis        | st of Tables                                                                            | . iii |

| 1 <i>A</i> | About This Guide                                                                        | 1     |

|            | 1.1 Purpose                                                                             | 1     |

|            | 1.2 Supported Products                                                                  | 1     |

|            | 1.3 Related Documents                                                                   | 1     |

|            | 1.4 Terminology and Abbreviations                                                       | 2     |

|            | 1.5 Support and Feedback                                                                | 2     |

| <b>2 l</b> | nstructions of FPGA Offline Programmer                                                  | 3     |

|            | 2.1 Overview                                                                            | 3     |

|            | 2.2 Instructions of Offline Programmer                                                  | 3     |

|            | 2.2.1 Software Download and Driver Installation                                         | 3     |

|            | 2.2.2 Configuration Interface                                                           | 4     |

|            | 2.2.3 Configure to Programmer                                                           | 6     |

|            | 2.2.4 Password                                                                          | 7     |

|            | 2.2.5 Program four FPGA devices Simultaneously                                          | . 10  |

|            | 2.2.6 Program One FPGA Automatically                                                    | . 11  |

|            | 2.2.7 Program Security key (GW2A)                                                       | . 12  |

|            | 2.3 Diagram of Programmer Interface Connection and Description of Voltage Configuration | า14   |

|            | 2.3.1 Programmer Interface Connection Diagram                                           | . 14  |

|            | 2.3.2 Voltage Configuration Jumper Diagram                                              | . 14  |

|            | 2.4 Instructions of FPGA Offline Programmer Firmware Update                             | . 15  |

|            | 2.5 Notes                                                                               | . 16  |

|            | 2.6 Main features are as follows                                                        | . 16  |

|            | 2.7 Specification and Parameter                                                         | . 17  |

|            | 2.8 Error code and Troubleshooting                                                      | . 17  |

## **List of Figures**

| Figure 2-1 Driver Installed Information                                 | 4  |

|-------------------------------------------------------------------------|----|

| Figure 2-2 Software Configuration Interface                             | 5  |

| Figure 2-3 Software Configuration Interface                             | 7  |

| Figure 2-4 Password Change Interface                                    | 8  |

| Figure 2-5 Password Change Completion Interface                         | 9  |

| Figure 2-6 Password Configuration Interface                             | 10 |

| Figure 2-7 Programmer Exterior                                          | 10 |

| Figure 2-8 Connecting Programmer to SocketBoard                         | 11 |

| Figure 2-9 Configuraton Interface of Programming Security key           | 13 |

| Figure 2-10 Diagram of Programmer Interface Connection                  | 14 |

| Figure 2-11 Diagram of vcc1 and vcc2 Configuration Interface            | 14 |

| Figure 2-12 Diagram of vcc1 and vcc2 Configuration Completion Interface | 15 |

| Figure2-13 Firmware Update                                              | 15 |

UG301-1.1E ii

## **List of Tables**

| Table 1-1 Abbreviations and Terminology                     | 2  |

|-------------------------------------------------------------|----|

| Table 2-1 Firmware and Matched Programmer Type              | 16 |

| Table 2-2 Reference Time of Programming                     | 16 |

| Table 2-3 Error Code Corresponding to the Fault Information | 17 |

UG301-1.1E iii

1 About This Guide 1.1 Purpose

## 1 About This Guide

## 1.1 Purpose

This guide includes two parts:

- 1. How to use FPGA offline programmer;

- 2. Functional description of Programmer.

## 1.2 Supported Products

This guide describes quad JTAG interfaces offline programmer, OP720-4 type.

The programmer in the guide applies to the following products: GW1N-1, GW1N-2, GW1N-4, GW1NR-4, GW1NZ, GW1N1S, GW1N-9, GW2A18.

#### 1.3 Related Documents

The latest user guides are available on our Website. Refer to the related documents at www.gowinsemi.com

- 1. DS100, GW1N series of FPGA Products Data Sheet

- 2. UG107, GW1N-1 Pinout

- 3. UG105, GW1N-2&2B&4&4B Pinout

- 4. <u>UG114</u>, GW1N-6&9 Pinout

- 5. DS117, GW1NR series of FPGA Products Data Sheet

- 6. UG116, GW1NR-4&4B Pinout

- 7. UG801, GW1NR-9 Pinout

- 8. DS841, GW1NZ series of FPGA Products Data Sheet

- 9. UG842, GW1NZ-1 Pinout

- 10. DS821, GW1NS series of FPGA Products Data Sheet

- 11. UG822, GW1NS-2 Pinout

UG301-1.1E 1(17)

## 1.4 Terminology and Abbreviation

The terminology and abbreviations used in this manual are as shown in below Table 1-1.

Table 1-1 Terminology and Abbreviations

| Terminology and Abbreviations | Meaning                       |

|-------------------------------|-------------------------------|

| DFU                           | Device Firmware Upgrade       |

| FPGA                          | Field Programmable Gate Array |

| JTAG                          | Joint Test Action Group       |

| ID                            | Identification                |

## 1.5 Support and Feedback

Gowin Semiconductor provides customers with comprehensive technical support. If you have any questions, comments, or suggestions, please feel free to contact us directly by the following ways.

Website: www.gowinsemi.com

E-mail:support@gowinsemi.com

+Tel: +86 755 8262 0391

UG301-1.1E 2(17)

# 2 Instructions of FPGA Offline Programmer

#### 2.1 Overview

Offline programmer is a device that programs GW1N(R) chips offline. It has the features of data confidentiality, portability, multi-path programming, etc. It can apply to rapidly large-volume production at the factory and is convenient for maintenance personnel to carry out. The offline programmer can simultaneously program four FPGA devices, and automatically detect device access and program in a single interface, which greatly increases the mass production rate.

The offline programmer encrypts and saves the data using an AES-128 advanced encryption algorithm, and the key is saved after several times of encrypting. AES is a set of internationally recognized, commonly used and secure encryption standards that ensure securely delivering data.

## 2.2 Instructions of Offline Programmer

The offline programmer can be configured using the offline programmer software, such as data stream file management, upper programming limit management, and programmer firmware upgrade. The software supports Windows 7 and above operating systems. After configuration, the offline programmer can be connected to the FPGA to program.

#### 2.2.1 Software Download and Driver Installation

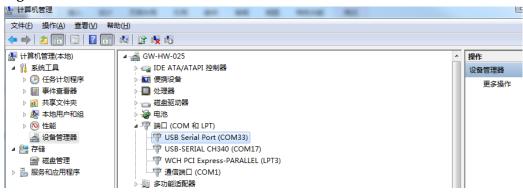

The software and driver package can be downloaded at Gowin website: <a href="https://www.gowinsemi.com/en/support/devkits\_detail/7/">https://www.gowinsemi.com/en/support/devkits\_detail/7/</a> or contact the local office or technical support center. Install the driver, and the path is driver/ gowin\_usb\_driver.exe. After installation, use USB cable to connect the programmer and computer, and USB Serial Port (COMxx)

UG301-1.1E 3(17)

appears on the port, that is, the driver is installed successfully, as shown in Figure 2-1.

#### Note!

If you have used Gowin USB programming download cable before, it does not need to install the driver

Figure 2-1 Driver Installed Information

## 2.2.2 Configuration Interface

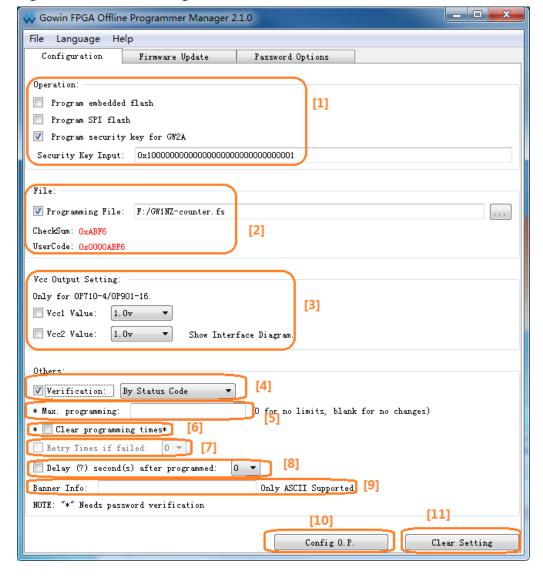

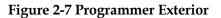

OPmanager.exe is the associated software in the "bin" directory. Open OPmanager.exe, and the configuration options are shown in Figure 2-2

UG301-1.1E 4(17)

Figure 2-2 Software Configuration Interface

- Operation: Program embeded flash, program SPI flash, or program security key. The checkd is the operation performed by the programmer. If you choose to program the security key (only the GW2A series is supported), you need to enter the security key, which cannot be changed after it is written.

- 2. Programming File: The selected one is GW1NZ.fs. Open the management tool and generate the key randomly, encrypt the data stream files and store them in the programmer.

- Vcc1 and vcc2 output setting requires manual adjustment of jumper. After adjustment, the boot interface will display the configured vcc1 vcc2 voltage.

UG301-1.1E 5(17)

The output can be: 1.2v 1.5v 1.8v 2.5v 3.3v, and the default is 1.0v without adjusting jumper. Vcc2 configuration is the same as vcc1

4. Verification: Status code, Read-back, and No verification.

#### Note!

- Status code: Determine whether the programming is successful or not according to the status code read from the FPGA after finishing programming data stream files.

- Read-back: Determine whether the programming is successful or not according to the consistency of writing and reading after finishing programming data stream files.

- No verification, that is, only prompts the finishing of programming

- 5. The max. programming times: If it sets 100, "programming times: Error" will pop up on the LCD of the offline programmer if the programming times are greater than 100. This is valid only if the password is configured correctly.

- 6. Clear programming times: Check to clear programming times, which is valid with password configuration.

- 7. Retry times if failed: Retry x times automatically if failed, and error will be reported if x times fails

#### Note!

Retry times settings are not supported for the time being

- 8. Delay after programmed: Delay x seconds after programmed, indicating the result of programming.

- 9. Configure to programmer: Configure the checked information items to programmer.

- 10. Customized information: Any entering customized character will be displayed on the programmer screen after configuration.

## 2.2.3 Configure to Programmer

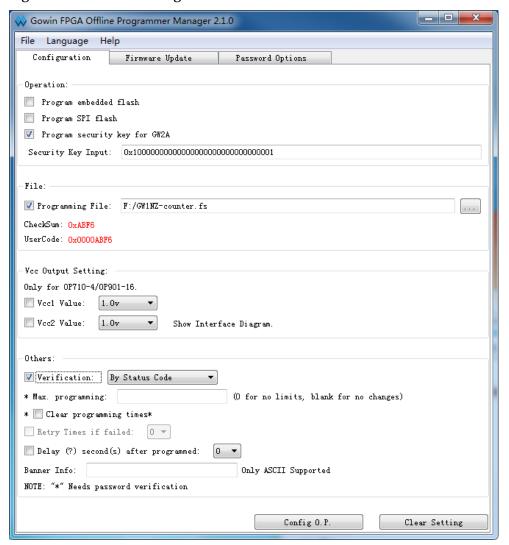

The associated software is required to configure the programmer. Open OPManaer.exe software to configure, as shown in Figure 2-3. The steps are as follows:

- 1. Select data stream file (Only supports .FS format at present).

- 2. Verification selection: Select according to the status code.

- 3. Set the max. programming times or leave it blank.

- 4. Click the "Config O.P." button.

- 5. Reboot the programmer after configuration.

UG301-1.1E 6(17)

For the item with \*, it needs correct password check to configure to the programmer. If the password is not correct, it will show that the password check fails, but the configuration of other items to the programmer will not be affected

Figure 2-3 Software Configuration Interface

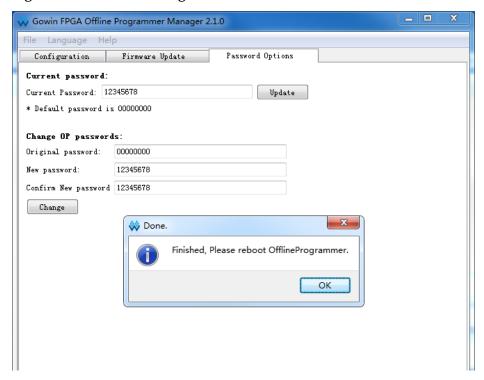

#### 2.2.4 Password

Configure the max. programming times and clear programming times, it needs to enter the password of the current offline programmer and update it to the local before configuring to the programmer. If the password is incorrect, there is no permission to configure the max. programming times and clear programming times. For the first time to use, steps are as follows:

- 1. When the new offline programmer is first used, the default factory password is 00000000.

- 2. Enter the original password 00000000, then enter the new password 12345678, confirm the password 12345678

UG301-1.1E 7(17)

The new password can be set to any 8 digits

- 3. Click "Change" to change the password of the offline programmer.

- 4. Click "Update" to obtain permission: Set the max. programming times and clear the programming times.

A password has been set for the programmer. The steps are as follows:

- 1. Enter the password of the programmer, such as: 1111111, click Update Local Password.

- 2. Configure the max. programming times and clear programming times.

- If the password is incorrect, the max. programming times and clearing programming times can not be configured, and other configuration items are not affected.

Figure 2-4 Password Change Interface

UG301-1.1E 8(17)

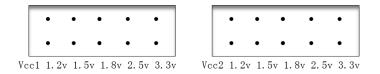

Gowin FPGA Offline Programmer Manager 2.1.0 File Language Help Configuration Firmware Update Password Options Operation: Program embedded flash Program SPI flash Program security key for GW2A ▼ Programming File: F:/GW1NZ-counter.fs CheckSum: OxABF6 × W Done. UserCode: 0x0000ABF6 Finished, Please reboot OfflineProgrammer. Vcc Output Setting: Only for OP710-4/OP901-ОК Vcc1 Value: 1.0 Vcc2 Value: 1.0v Others: ▼ Verification: By Status Code ▼ (O for no limits, blank for no changes) \* Max. programming: 100 \* 🦳 Clear programming times\* Retry Times if failed: 0 🔻 Delay (?) second(s) after programmed: Banner Info: Only ASCII Supported NOTE: "\*" Needs password verification Config 0.P. Clear Setting

Figure 2-5 Password Change Completion Interface

UG301-1.1E 9(17)

\_ D X Gowin FPGA Offline Programmer Manager 2.1.0 File Language Help Password Options Configuration Firmware Update Current password: Current Password: 12345678 Update \* Default password is 00000000 Change OP passwords: Original password: 00000000 New password: 12345678 Confirm New password 12345678 Change

Figure 2-6 Password Configuration Interface

## 2.2.5 Program four FPGA devices Simultaneously

UG301-1.1E 10(17)

OP720-4

offline

programmer

JTAG

FPGA

FPGA

JTAG

FPGA

FPGA

FPGA

FPGA

FPGA

FPGA

FPGA

Figure 2-8 Connecting Programmer to SocketBoard

The four FPGAs are of the same type.

The quad JTAG programming interfaces share the TCK, TDI, and TMS signal lines. After the programmer sends commands, the four FPGAs responds and can be programmed simultaneously. Operation steps of programing four FPGA devices simultaneously are as follows:

- Power up and boot the programmer (support USB power supply or 5V power supply);

- Connect four FPGAs to the programmer;

- Press the green Program key, the screen displays detecting the device and the corresponding ID CODE is displayed after the device is detected. The corresponding indicator turns green after the programming is done successful.

#### Note!

In this mode, n (<=4) FPGAs can be programmed if they are connected. The programming interfaces of 1.2.3.4 can be selected optionally.

## 2.2.6 Program One FPGA Automatically

In the automatic programming mode, the programmer can automatically detect the new FPGA. It will program automatically if a new

UG301-1.1E 11(17)

FPAG is connected. Currently, automatically programming only supports one FPGA, and only interface 1 of the programmer supports detecting and programming automatically. Operation steps of programing one FPGA automatically are as follows:

- Power up and boot the programmer (Support USB power supply or 5V power supply);

- 2. "AUTO-PRO-MODE" will be displayed after pressing the program key for 5 seconds, and then the programmer enters the auto programming mode;

- 3. Connect one FPGA to interface 1;

- 4. The screen displays detecting the device and the corresponding ID CODE is displayed after the device is detected. The corresponding indicator turns green after the programming is done successful.

- 5. Disconnect the FPGA from the interface1, and then connect it to the interface 1 again. The programmer will automatically program the stream file to the FPGA device, and you do not need to press the green programming key.

#### Note!

The automatic detection is used to detect whether there is a device connecting the programmer; if a device is connected, it will be programmed automatically. If not, the programmer will continue detecting and waiting for the new device.

### 2.2.7 Program Security key (GW2A)

Only support single interface to program the security key, and the first access one is valid.

UG301-1.1E 12(17)

Figure 2-9 Configuraton Interface of Programming Security key

The steps are as follows:

- Check "Program security key for GW2A" (AES) and enter the security key;

- 2. Click "Config O.P."

- 3. Reboot the device;

- 4. Connect the FPGA to the first interface;

- 5. Press program, after programming finishing, it can not program again.

UG301-1.1E 13(17)

## 2.3 Diagram of Programmer Interface Connection and Description of Voltage Configuration

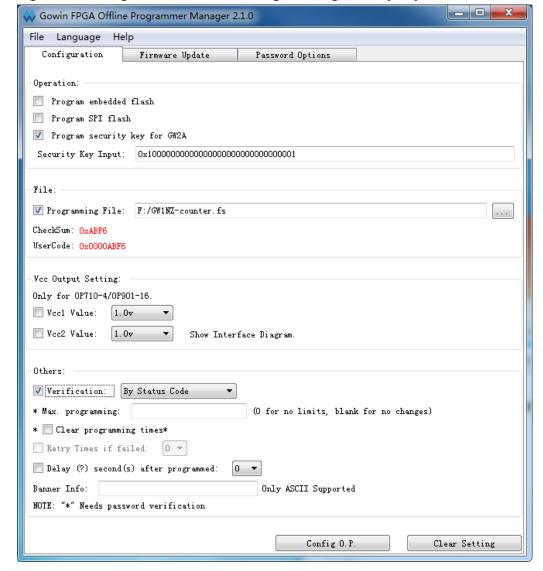

### 2.3.1 Programmer Interface Connection Diagram

Figure 2-10 Diagram of Programmer Interface Connection

#### Note!

- 3.3V is the voltage outputting to the FPGA device.

- EVCC is the input voltage, which is the VCCIO voltage of the FPGA chip.

- Vcc1/2 is configurable output voltage.

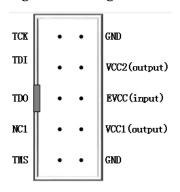

## 2.3.2 Voltage Configuration Jumper Diagram

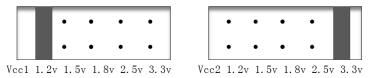

Figure 2-11 Diagram of vcc1 and vcc2 Configuration Interface

The programmer can configure VCC output voltage by jumper. If jumper is not used, the default output is 1.0v. The output can be configured as 1.2v, 1.5v, 1.8v, 2.5v, 3.3v by using jumper. As shown in Figure 2-12, vcc1 jumper is inserted at1.2v and vcc2 is inserted at 3.3v, that is, vcc1 is configured as 1.2v and vcc2 as 3.3v. After the jumper is inserted, restart the programmer, and the second interface of the start will display vcc1:1.2v and vcc2:3.3v.

UG301-1.1E 14(17)

Figure 2-12 Diagram of vcc1 and vcc2 Configuration Completion Interface

## 2.4 Instructions of FPGA Offline Programmer Firmware Update

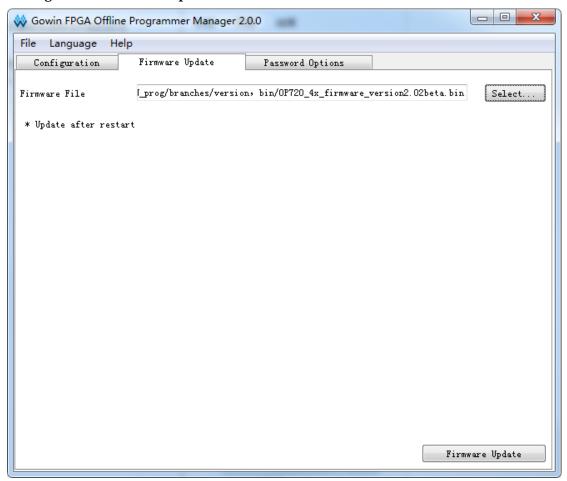

Figure 2-13 Firmware Update

The firmware update steps are shown below:

- 1. Connect the programmer to PC with USB cable;

- 2. Select firmware to update, such as OP720\_4x\_firmware\_version2.0beta.bin.

- 3. Click the firmware update, wait for the prompt box to restart device, and reboot the offline programmer to complete the update.

UG301-1.1E 15(17)

Firmware update is to update the offline programmer so that the latest features can be used

The obtaining address of the latest firmware:

https://www.gowinsemi.com/en/support/devkits\_detail/7/

The firmware to download should match the offline programmer, as shown in Table 2-1.

Table 2-1 Firmware and Matched Programmer Type

|                                    | <b>71</b>               |

|------------------------------------|-------------------------|

| Firmware Name                      | Matched Programmer Type |

| OP710_4x_firmware_version1.9x.bin  | OP710-4 (Blue Shell)    |

| OP720_4x_firmware_version2.0x.bin  | OP720-4 (Balck Shell)   |

| OP901_16x_firmware_version2.0x.bin | OP901-16                |

#### 2.5 Notes

- 1. If the firmware is upgraded with mismatched firmware, resulting in abnormal programmer, it needs to follow the steps as below to repair:

- a). The programmer powers off and shuts down

- b). Press the programming button to start and the indicator turns red

- c). Select the correct firmware and re-upgrade.

- When multiple devices are programed simultaneously, only the same series of devices are supported. For example, all the GW1N-1 devices or all the GW1N-4 devices.

- 3. The data stream file is configured in the offline programmer. Select the FPGA to be programmed according to the screen prompt: "currently support: GW1N(R)-x", to avoid other damage to the FPGA.

## 2.6 Main features are as follows

Power Supply

- Working voltage: DC5V±10%

- Power: 0.75 W

- Output voltage: Adjustable

Memory

Internal memory: 8MByte

Reference time of programming

#### **Table 2-2 Reference Time of Programming**

| Chip Type Supported | Programming Time (ms) |

|---------------------|-----------------------|

| GW1N-1              | 5312                  |

| GW1N-2              | 5312                  |

| GW1N(R)-4           | 5312                  |

| GW1N(R)-9           | 6278                  |

| GW1NZ               | 4600                  |

UG301-1.1E 16(17)

| Chip Type Supported | Programming Time (ms) |

|---------------------|-----------------------|

| GW1NS-2             | 4500                  |

- In JTAG mode, the data can be programed into the internal flash of the FPGA.

- Programming time is the total time of erasing the internal flash and successfully program the stream file into the FPGA internal flash. Program one FPGA and program four FPGAs requires the same time.

Supporting programming devices: GW1N(R)-1, GW1N(R)-2, GW1N(R)-4, GW1N(R)-4, GW1N(R)-6, GW1N(R)-9, GW1NZ and GW1N1S. vcc1 and vcc2 output voltage can be configured as: 1.0v, 1.2v , 1.5v , 1.8v, 2.5v and 3.3v.

## 2.7 Specification and Parameter

Working environment: 0-60<sup>°</sup>C

Frame Size: 120 mm \* 106 mm \* 26 mm

Screen: distinguishability (128\*160) size (32mm\*38mm)

Net weight: 350g.

## 2.8 Error code and Troubleshooting

After programming or if programming is successful, it will prompt: Programmed successfully and displayed STA:0x1f020 or STA:0x3f020. If the device is abnormal, an error code will be reported, and the error code corresponding to the fault information is shown in Table 2-3.

Table 2-3 Error Code Corresponding to the Fault Information

| Error Code | Fault Inforamtion          | Troubleshooting                         |

|------------|----------------------------|-----------------------------------------|

| E01        | POR error                  |                                         |

| E02        | GoWin VLD error            |                                         |

| E03        | Device error               | Detects whether the access device       |

| E04        | No access device           | Check whether the device is             |

| E05        | Data stream file failed to | Reconfigure the data stream file to the |

| E06        | Programming failure        | Re - programming, retry 3 times         |

| E07        | The programming is         | JTAG reuse, read back information       |

UG301-1.1E 17(17)